Comparison Measurements of Natural Constants Based on Laser-Focused Atomic Deposition and Extreme Ultraviolet Interference Lithography.

Abstract

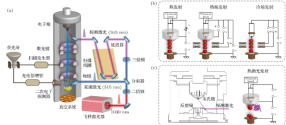

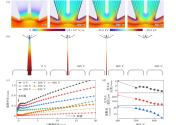

Traceability is the foundation of accuracy and consistency in dimensional metrology. Meter in the International System of Units is defined and reproduced by natural constants, and comparing the differences in traceability approaches based on different natural constants can better understand the real size of manufacturing structures. This paper compares the consistency of three traceability approaches based on chromium atomic transition wavelength, iodine-stabilized laser wavelength (top-down approach), and silicon lattice spacing (bottom-up approach) in nanoscale dimensional metrology. The measured objects for comparison are silicon gratings manufactured by laser focused atomic deposition (LFAD) and extreme ultraviolet interference lithography (EUV IL), and the pitch of the silicon gratings can be traceable to the transition wavelength of chromium (7S3→7P4, lambda=425.5533 nm). For the silicon grating manufactured by LFAD and EUV IL at diffraction order m=1, the expected pitch of the silicon grating is lambda/4. The pitch of the silicon grating is measured using top-down (metrological AFM) approach, and the deviation between the measured result and the pitch based on the transition wavelength of chromium is 0.1 nm. For the silicon grating manufactured by LFAD and EUV IL at diffraction order m=2, the expected pitch of the silicon grating is lambda/8. This silicon grating is measured using bottom-up approach, and the deviation between the measured result and the pitch based on the transition wavelength of chromium is 0.2 nm. This research provides a feasible solution for integrating various measurement methods or different traceability approaches at nanoscale, and demonstrating the potential and feasibility of a nanoscale dimensional metrology traceability chain based on self-traceable gratings.