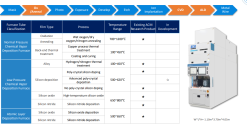

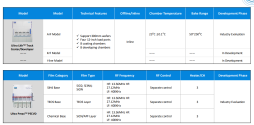

The United States has increased its control over semiconductors in China, and domestic substitution of RF power supplies has accelerated

U.S. sanctions on technology blockades have promoted the accelerated verification of domestic RF power supplies. The replacement of RF power supplies has a great impact on the process. Customers have previously had little willingness to replace, but the "semiconductor manufacturing" end-use restrictions introduced by the United States in October 2022 further restricted the development of domestic semiconductors. RF power supplies have become one of the "neck" links, and the demand for domestic substitution is urgent. Domestic equipment companies are facing an increasingly close risk of supply interruption, prompting equipment-end customers to accelerate domestic substitution. RF power supply is one of the semiconductor equipment components with high technical barriers. To achieve high power and high efficiency, manufacturers need to have a deep technical accumulation of internal circuit and structural design, and cooperate with customers to continuously debug.