With a total investment of 5 billion yuan, the AiSi Technology Park Packaging and Testing Project officially broke ground

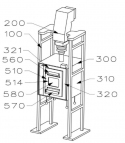

AiSi Technology Park has a total investment of 5 billion yuan, covers an area of 121 mu, has a construction area of about 200,000 square meters, and is equipped with high-rise factories, comprehensive supporting buildings, semiconductor professional factories and related supporting facilities. As the base camp of AiSi Technology, the project will build a headquarters, four manufacturing bases, and two R&D centers. At the same time, it will introduce semiconductor advanced equipment industry, semiconductor material cutting-edge R&D companies, and chip system integration and sales projects to create a semiconductor packaging and testing industry chain park supported by R&D.

AiSi Technology spans the two fields of "design" and "packaging and testing" in the semiconductor chip industry. In the field of packaging and testing, the existing Xuzhou packaging plant mainly uses wire bonding packaging forms such as SOP/SOT, QFN, DFN, high-end SIP system-level packaging, and wafer-level packaging such as WLCSP as the main packaging forms. In December 2022, "Anhui AiSi Semiconductor Co., Ltd." was established in Fuyang, Anhui as a professional testing plant. In February 2023, "Anhui AiSi Semiconductor Co., Ltd."