Recently, Eswi Computing's RISC-V core R500A passed the ASIL-B functional safety certification issued by TÜV Rheinland, Germany, becoming the world's first RISC-V core to pass the TÜV Rheinland ASIL-B functional safety certification.

As a century-old authority in the field of functional safety (established in 1872), TÜV Rheinland has established strict standards for many high-security scenarios such as automotive electronics with its profound background. Its certification process is extremely strict, covering in-depth testing of the entire process from design to finished products. It is an internationally leading provider of testing, inspection, certification, training, and consulting services. This certification marks that Eswin Computing R500A has entered the first-tier camp in the field of functional safety, providing developers with a new choice of kernel architecture that is both open and reliable.

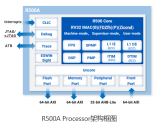

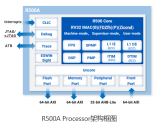

Eswin Computing R500A is a high-performance 32-bit RISC-V automotive-grade real-time kernel product. Its CoreMark performance is as high as 5.794 CoreMarks/MHz, which means that it can achieve a computing performance of about 5.794 points per MHz, and the DMIPS in legal and best reach 2.552 and 7.297DMIPS/MHz respectively. With its streamlined and efficient architecture design, R500A excels in real-time, low latency and security isolation.

High-security critical areas such as automotive braking systems and precision industrial control have long been dominated by closed-source technology solutions, which have formed a technical application barrier. With its open and flexible architecture design, Eswin Computing's RISC-V core R500A can adapt to the diverse needs of different customers, help automakers and industrial customers accelerate technology implementation, and bring a new choice with both customization and cost advantages to the industry.

As early as September 28, 2022, Eswi Computing obtained the ASIL-D functional safety system certification (the highest level of automotive safety integrity), which covers the entire technical process from kernel design, system development to verification tools. This certification fully proves that the technical solution built on the RISC-V architecture has the core capabilities to support "zero fault tolerance" extreme scenarios such as autonomous driving and avionics. This not only lays a solid foundation for RISC-V to enter high-barrier markets such as L4/L5 autonomous driving and medical devices in the future, but also means that the application potential of the RISC-V architecture in the fields of high security and high reliability has been fully released, and it is expected to promote the iterative upgrade of relevant industry technical standards.