Heyan Technology won the second phase of investment from the National Fund to focus on semiconductor grinding equipment

On December 29, 2022, Heyan Technology was invested by the National Integrated Circuit Industry Investment Fund Phase II Co., Ltd. (National Large Fund Phase II).

It is reported that this round of financing is the B+ round of financing of Heyan Technology, and the industrial and commercial change registration has been completed.

Established in 2011, Heyan Technology is a company specializing in the research and development, sales, consulting and service of semiconductor grinding equipment, focusing on silicon wafers, glass, ceramics, quartz, lithium niobate, silicon carbide, resin and other hard Precision cutting of brittle materials.

The company's main business is 6~12 inches DS series precision dicing machine, JS series automatic cutting and sorting machine and other semiconductor-specific precision cutting equipment, which are widely used in the manufacturing fields of integrated circuits, discrete devices, optoelectronic devices and sensitive components.

Chemical Mechanical Polishing (CMP) is a key process to achieve global planarization of wafers. The CMP process runs through silicon wafer manufacturing, integrated circuit manufacturing, packaging and testing. Polishing fluid and polishing pads are the core consumables of the CMP process, accounting for more than 80% of the CMP material market. The CMP materials and equipment companies represented by Dinglong and Huahai Qingke have attracted the attention of the industry.

The target is the core raw material for the preparation of functional thin films. It is mainly used in semiconductors, panels, photovoltaics and other fields to achieve functions such as conduction or barrier. Among the major semiconductor materials, the target is the one with the highest degree of localization. Breakthroughs have been made in the field of domestic aluminum, copper, molybdenum and other target materials. The main listed companies include Jiangfeng Electronics, Youyan New Materials, Ashichuang, Longhua Technology, etc.

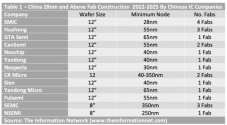

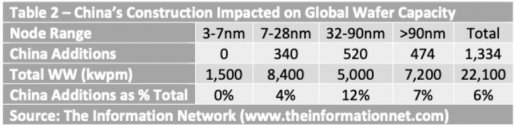

The next three years will be a period of rapid development of China's semiconductor manufacturing industry. Enterprises such as SMIC, Huahong Grace, Yangtze Memory, Changxin Storage, and Silan Micro will accelerate production expansion. Geke Micro, Dingtai Jiangxin, and China Resources Micro The 12-inch wafer production line deployed by the company will also be put into production one after another, which will bring huge demand for CMP materials and targets.

Under the new situation, the security of the supply chain of domestic fabs is becoming more and more important, and it is imperative to cultivate stable local material suppliers, which will also bring huge opportunities to domestic suppliers. The successful experience of target materials will also provide reference for the localization development of other materials.