According to scitechdaily, a Chinese research team composed of institutions such as Huazhong University of Science and Technology, Shanghai Jiaotong University, University of Electronic Science and Technology of China and Nankai University has recently successfully developed the world's first programmable single-chip all-optical signal processing (AOSP) chip, which can support optical filtering, signal regeneration and logical operations, breaking the limitation of traditional silicon photonics requiring "optical-electrical-optical (OEO)" conversion, allowing data to maintain the optical signal state from input to output, and moving towards a new high-speed computing architecture that does not require switches.

Breakthrough in programmable AOSP chip development

Breakthrough in programmable AOSP chip development

A research team consisting of Professor Zhang Xinliang of Huazhong University of Science and Technology, Professor Su Yikai of Shanghai Jiaotong University, Professor Qiu Kun of University of Electronic Science and Technology of China, and Academician Zhu Ninghua of Nankai University has successfully developed a monolithic integrated programmable all-optical signal processing (AOSP) chip. The chip supports key functions such as optical filtering, signal regeneration, and logic operations. The project originated from a national project aimed at developing silicon-based reconfigurable AOSP technology.

By leveraging the core advantages of silicon photonics, such as CMOS compatibility, minimal signal loss, compact form factor, and strong optical nonlinearities, researchers have produced a chip that can meet the stringent requirements of next-generation optical networks.

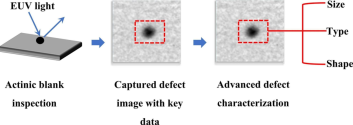

These include high-speed data transmission, compatibility with advanced modulation formats, and support for wavelength-transparent operation. The team has experimentally verified the chip's ability to perform dynamic filtering, logic calculations, and signal regeneration, laying a solid foundation for its use in cutting-edge applications such as optical communications, advanced computing, imaging, and sensing.

Overcoming the limitations of silicon photonics

There are several technical barriers to developing a programmable all-optical signal processing (AOSP) platform on silicon-on-insulator (SOI) technology. A major issue is that silicon exhibits carrier-related effects, particularly two-photon absorption (TPA) and free-carrier absorption (FCA), which limit the amount of power available for nonlinear interactions, thereby weakening these effects. In addition, the high refractive index contrast in silicon leads to severe confinement of the optical field, which increases scattering losses, complicates the precise control of light propagation, and introduces significant optical and thermal crosstalk.

To overcome these limitations, researchers have introduced improved fabrication methods, innovative device structures, and novel materials. One key advance involves the development of ultra-low-loss silicon waveguides and high-quality microresonators through enhanced manufacturing techniques. These components enable integrated photonic filters that offer wide, reconfigurable bandwidths and tunable free spectral ranges, allowing highly flexible and precise manipulation of input optical signals.

Chip performance indicators and future prospects

This study highlights key advances in the development of programmable AOSP chips. Through structural and material innovations, key challenges in building large-scale integrated AOSP photonic chips, such as high transmission loss, weak nonlinear effects, limited light field control, and severe optical, electrical, and thermal crosstalk, were addressed. The ultra-low-loss silicon waveguide had a loss as low as 0.17 dB/cm and a Q factor as high as 2.1106.

The research team has achieved advanced integrated filters with bandwidths that can be tuned from 0.55 pm to 648.72 pm (i.e., over three orders of magnitude) and FSRs that can be tuned from 0.06 nm to 1.86 nm (30 times). Absolute FWM conversion efficiencies as high as 12 dB have been demonstrated, which is critical to ensuring the success of high-performance logic and regenerative operations.

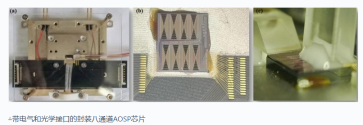

An eight-channel multifunctional single-chip integration of filtering, logic, and regeneration has been achieved, integrating 136 devices (including filters, logic gates, regenerators, gratings, MMIs, electrodes, etc.) on a single chip. It has been proven that the total signal processing capability is up to 800 Gb/s (operating at 100 Gb/s per channel), and it can accommodate multiple modulation formats, including DPSK and OOK. A complete set of CLUs has been generated for logic operations, and QPSK regeneration has been proven to improve receiver sensitivity by more than 6dB. By leveraging advanced optoelectronic packaging technology, chip-level routing and processing of multi-channel signals have been verified.

Due to the inherent ultrafast characteristics of optical Kerr nonlinearity (on the femtosecond time scale), these efforts lay the foundation for the design and manufacture of faster large-scale silicon-based AOSP chips. Looking ahead, improvements in nanofabrication technology, new materials, and packaging processes are expected to further improve the performance and flexibility of AOSP chips, providing more efficient optical solutions for high-speed communications and advanced computing, and the optical components on the chip will move from supporting roles to leading roles. If logical operations, data routing, and even memory access can be completed in the optical domain in the future, whether switches are still necessary components will inevitably become the focus of industry discussion.